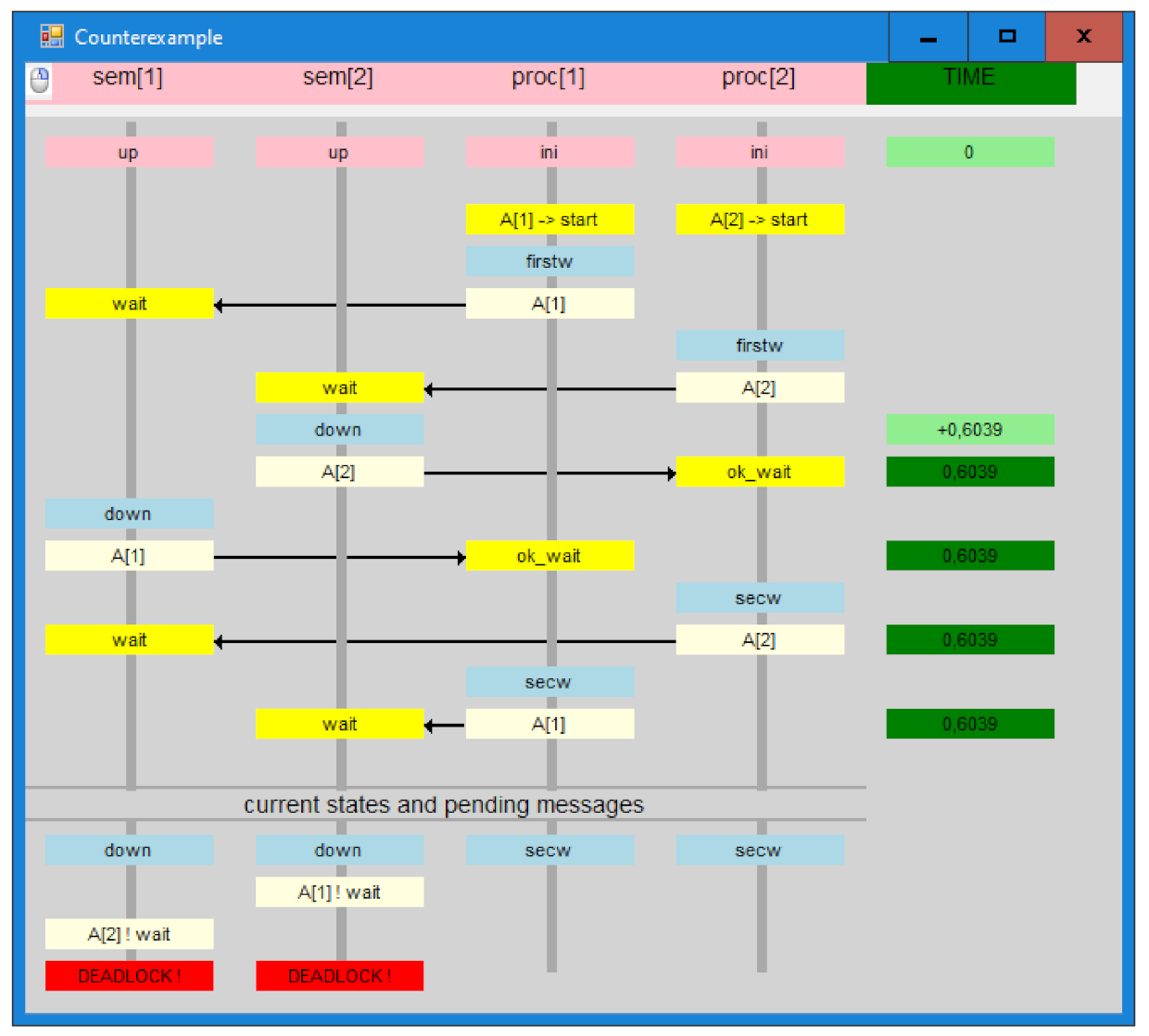

modeling - UPPAAL: Invariants violated but none have been explicitly set - how to resolve deadlock? - Stack Overflow

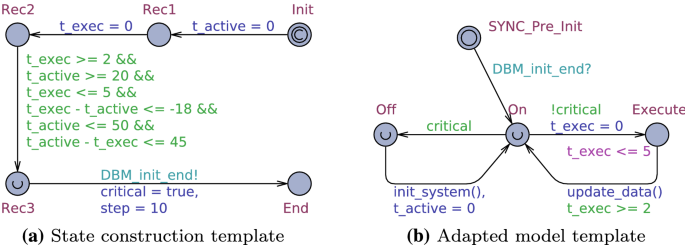

Integration of iUML-B and UPPAAL Timed Automata for Development of Real-Time Systems with Concurrent Processes | SpringerLink

modeling - UPPAAL: Invariants violated but none have been explicitly set - how to resolve deadlock? - Stack Overflow

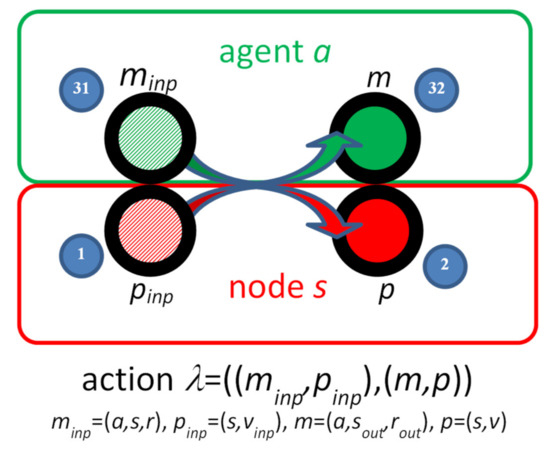

Sensors | Free Full-Text | Modeling and Verification of Asynchronous Systems Using Timed Integrated Model of Distributed Systems

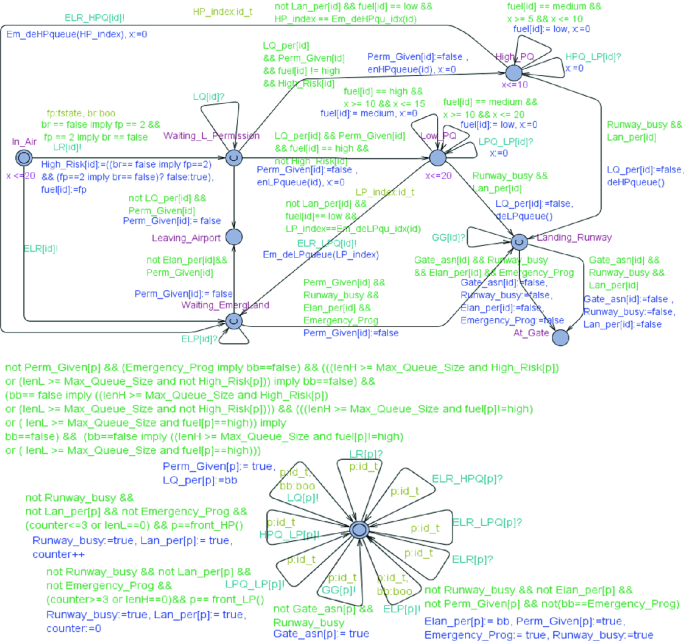

Timed automata based modeling and verification of denial of service attacks in wireless sensor networks

Modeling and Verification of Asynchronous Systems Using Timed Integrated Model of Distributed Systems